Silicon Photonics for Performance-Optimized Multi-Haul

Introduction

In the introductory Part 1 of this blog series, we described general trends that are guiding design and investment decisions for next-generation coherent solutions to meet the constant growth of bandwidth demand. In this blog, I discuss why silicon photonics (SiPh) offers many advantages for performance-optimized multi-haul coherent solutions.

SiPh Critical for Small Sizes and High Baud Rates

SiPh has been utilized for most of the 400G MSA form-factor pluggable coherent modules available today because it offers excellent performance while enabling small footprint QSFP-DD and OSFP form factors with tight power requirements. Due to its high temperature tolerance and non-hermetic nature, SiPh can be co-packaged with the coherent digital signal processor (DSP) ASIC which preserves high speed analog signal integrity between these devices. In addition, SiPh leverages well established CMOS fabrication processing technology and volume manufacturing practices, enabling it to scale to meet the accelerated lifecycle requirements of these volume applications.

According to LightCounting, more than 250,000 pluggable modules supporting interoperable protocols are expected to be deployed in 2023. As discussed in Part 1, as the gap to Shannon’s Limit narrows, the proportion of additional capacity achieved from additional digital signaling processing power becomes smaller. As a result, the improvements in network efficiency become driven by changes in architecture, improvements in power and size, as well as doubling baud rate with each new generation (see previously published blog on baud rate classes here). These higher baud rate designs are more sensitive to impairments along the electrical paths between the coherent DSP ASIC, modulator drivers, transimpedance amplifiers (TIAs) and the silicon photonic integrated circuit (PIC).

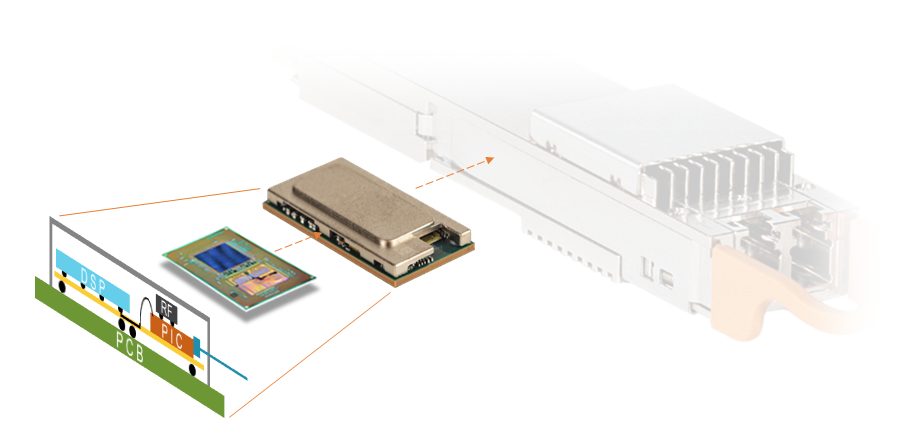

Acacia’s SiPh optimizes high-speed RF electrical component interconnects to achieve 120Gbaud+ baud rates. A chain is only as strong as its weakest link. Thus, even with the best high-speed capable RF electrical/opto-electronic components, when these components are electrically connected, signal degradation can limit the solution’s performance at high baud rates. By using a common silicon platform, the mixed signal RF components can be tightly integrated with the silicon PIC and DSP, which minimizes electrical impairments that degrade the performance. Using fiber coupling, these components can be kept away from the laser to avoid thermal effects. Acacia has successfully demonstrated this across its wide range of high-performance coherent products, including those for subsea applications, which share these design traits.

Figure 1. Acacia’s 3D Siliconization enables a tightly integrated design that minimizes electrical impairments that affect high baud rate performance.

While alternative solutions utilizing indium phosphide (InP) may implement the laser and optical gain together with the high-speed optics, due to the thermal sensitivity of these components, they need to be packaged separately from the DSP. This results in impairment of the high-speed RF electrical connections which can limit the solution’s overall performance at higher baud rates.

Acacia’s 3D Siliconization leverages high-volume processes already established in the semiconductor industry to manufacture compact and non-hermetic coherent modules with high-performance electrical RF interconnects. 3D Siliconization takes advantage of mature silicon photonics technology and in-house expertise.

As we move towards 120+ Gbaud requirements (Class 3) and beyond, 3D Siliconization offers the critical improvements needed for coherent interfaces operating at these baud rates.

Leveraging a Common Foundation

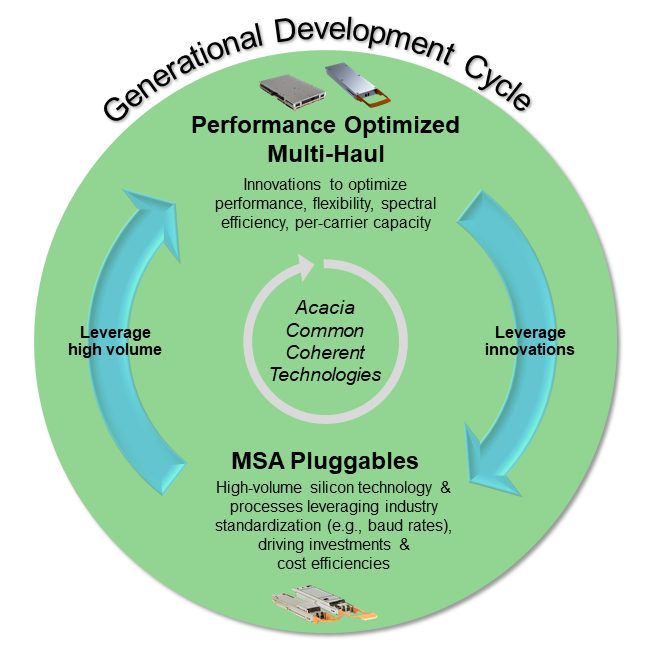

For multiple product generations, Acacia has been leveraging common development based on silicon for both performance-optimized multi-haul and high-volume MSA pluggable solutions. SiPh core technology is a key element in leveraging pluggable volume driven designs and processes to benefit multi-haul solutions, and vice-versa.

Figure 2. Generational development cycle of coherent solutions leveraging common development based on silicon for performance-optimized multi-haul and high-volume MSA pluggables.

While competing innovations are bound to continue as bandwidth demand increases, Figure 2 illustrates that with higher baud rate requirements around the corner, underlying technology choices do matter when it comes to overall design efficiencies and time-to-market. The approach of common development based on silicon has already been benefiting both performance-optimized and MSA pluggable coherent products in currently shipping Class 2 (64 Gbaud) category.

Stay Tuned for Part 3

In our next blog in this series, I discuss the coherent operating sweet spot, and how a crossover point in coherent shipments amplifies the significance of the coherent generational development cycle.

Learn More About the Considerations Driving Next Generation Multi-Haul Solutions: